在高速和高频电路的应用中,PCB的阻抗控制至关重要。对于PCB制造商而言,确保阻抗符合设计要求,不仅关乎信号完整性,也直接影响产品的电磁兼容性(EMC)和整体可靠性。本文将从PCB制造的角度,详细探讨阻抗控制的技术核心和关键影响因素。

阻抗(Z)是交流电路中电流受到的总对抗,单位为欧姆(Ω)。它由电阻(R)和电抗(X)组成,其中电抗又分为电感抗(XL)和电容抗(XC)。在PCB的传输线中,阻抗主要取决于信号走线的几何结构、材料的介电特性以及频率等因素。

对于PCB制造来说,阻抗控制的主要目的是保证信号传输的完整性,减少信号反射和损耗,从而提高电子产品的性能和稳定性。在高频信号传输中,阻抗的不匹配可能会导致:

信号反射和振铃,影响高速信号的可靠性;

增加EMI(电磁干扰),影响产品的电磁兼容性;

数据误码率上升,影响通信系统的稳定性;

信号衰减加剧,影响长距离传输的效果。

在高频和高速PCB应用中,材料的选择至关重要。常见的材料及其特点如下:

FR4:常见的PCB材料,成本低,但Dk值较高,适用于中低速应用。

Rogers4350B:低Dk,低损耗,适用于5G通信、微波和雷达系统。

IsolaITeraMT40:低损耗,Dk值稳定,适用于高速信号传输。

PanasonicMegtron6:高可靠性,适用于数据中心、光网络等高速应用。

在PCB制造过程中,影响阻抗的关键因素主要包括走线宽度、铜厚度、介电厚度、介电常数(Dk)、传输线类型、阻焊层的影响、层间对准精度、蚀刻工艺控制等。这些因素共同作用,决定了PCB的阻抗特性,从而影响信号完整性和系统性能。下面详细解析这些因素在PCB制造中的影响。

走线宽度决定了阻抗值,宽度越窄,阻抗越高;宽度越宽,阻抗越低。制造过程中,以下因素可能影响最终走线宽度:

蚀刻工艺:横向腐蚀可能导致实际宽度偏差,设计时需预留补偿量。

光刻精度:曝光与显影影响细线控制,HDI PCB尤为关键。

铜厚影响:铜层越厚,侧蚀越明显,需精准补偿以确保阻抗稳定。

常见阻抗公差控制在±10%,但5G通信、高速服务器等高端应用可能要求更严格,例如±5%。

铜厚(单位:oz,1oz = 35µm)影响传输线的直流电阻和交流阻抗。较厚的铜降低电阻,同时也降低阻抗。

铜厚增加,阻抗降低:电阻和等效电感减少,导致阻抗下降。

阻抗计算需考虑铜厚:标准铜厚一般为 0.5oz(17.5µm)、1oz(35µm)、2oz(70µm),高功率PCB可能需 3oz 或更厚。

电镀影响外层铜厚:多层板外层铜厚会因电镀增加,计算阻抗时需考虑这一因素。

深圳普林电路采用自动光学检测(AOI)和厚度测量仪监测铜厚,确保阻抗精度在容差范围内。

介电厚度是指信号层与参考地/电源层之间的绝缘层厚度。它直接影响传输线的分布电容和阻抗:

介电厚度增加,阻抗升高:较厚的介电层会增加信号与参考平面之间的距离,从而提高阻抗。

制造中的厚度变化:由于压合过程中的树脂流动、叠层结构的稳定性,实际介电厚度可能与设计值存在偏差,因此需要严格控制压合工艺,以确保阻抗一致性。

多层板中的一致性问题:对于高层数PCB,层间介电厚度的均匀性至关重要。如果厚度不均,会导致不同区域的阻抗不一致,影响信号传输。

深圳普林电路在层压前通常会进行介电材料厚度测量,并在阻抗测试时进行补偿,以确保最终阻抗值符合规格要求。

介电常数(Dk)决定了信号在介质材料中的传播速度。常见的PCB基材Dk值如下:

FR4标准材料:Dk≈4.2~4.7

高速材料(如Rogers4350B):Dk≈3.48

超高频微波材料(如TaconicRF35):Dk≈3.5

Dk对阻抗的影响表现为:

较高的Dk降低阻抗:因为Dk增加会提高分布电容,从而降低阻抗。

Dk的频率依赖性:FR4的Dk随频率增加而下降,而Rogers等高端材料的Dk更加稳定,适用于高速设计。

制造过程中的Dk一致性:为了确保Dk稳定性,PCB厂商通常会在材料采购时选择具有严格Dk公差的基材(如±0.02),并在生产过程中进行Dk测试,以避免阻抗偏差。

不同类型的传输线结构对阻抗的影响不同,主要包括:

微带线:信号走线位于最外层,下面是介电层和接地层。阻抗计算相对简单,但容易受到外部环境(如阻焊层)的影响。

带状线:信号走线被两层介质包围,介电环境更加均匀,因此信号完整性更好,适用于高频应用。

共面波导:信号线旁边有地线,以增强屏蔽效果,适用于射频和微波电路。

制造过程中,不同传输线的加工精度要求不同。例如,带状线对介电层厚度的控制要求更高,而共面波导则要求地线与信号线的间距高度一致,以确保良好的阻抗匹配。

在微带线结构中,阻焊层的存在会影响信号走线的有效介电常数(Dk_eff),从而影响阻抗:

无阻焊层的PCB阻抗较高,因为信号直接暴露在空气中,而空气的Dk≈1。

带阻焊层的PCB阻抗降低,因为阻焊层的Dk通常比空气高(Dk≈3.0~4.0),会降低整体阻抗。

为了减少阻焊层对阻抗的影响,PCB制造商可能会调整走线宽度或采用特殊的阻抗补偿方法,例如在阻抗计算时考虑阻焊层的Dk。

多层PCB制造中,各层之间的对准误差(层间偏差)会影响阻抗一致性:

对准偏差过大会影响带状线和差分对的阻抗匹配,导致信号完整性问题。

高精度对准(±25µm以内)可以确保阻抗一致,常见于高端通信和射频PCB制造中。

采用先进的光学对准技术(如激光对位)和Xray检测设备,有助于减少层间偏差,确保阻抗控制的精确度。

蚀刻是PCB制造中的关键步骤,影响最终走线宽度、边缘形状和阻抗:

侧蚀(Undercut):会减少有效走线宽度,从而增加阻抗。

线形优化:先进的蚀刻工艺(如V型或梯形线)可以减少阻抗变化,提高信号完整性。

深圳普林电路通过优化蚀刻参数、使用精确的曝光显影技术,并结合自动检测手段,可以有效控制蚀刻质量,确保阻抗的一致性。

深圳普林电路深知阻抗控制对高速、高频PCB性能的重要性。从走线宽度、铜厚、介电常数到层叠结构,每一个因素都直接影响信号完整性和产品可靠性。我们通过高精度蚀刻技术、先进电镀工艺、严格的厚度监控,以及自动光学检测(AOI)等手段,确保每块PCB的阻抗在严格的公差范围内。凭借成熟的制造经验和精密的工艺控制,我们为5G通信、数据中心、汽车电子等高端应用提供高质量的阻抗控制方案,助力客户实现卓越的产品性能。

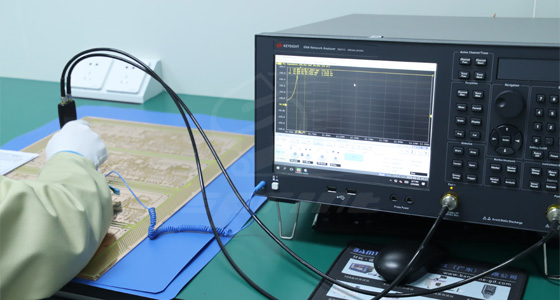

深圳普林实验室拥有业界领先的KEYSIGHT牌高精度阻抗测试仪,频率20GHZ,配置特殊测试探头,可以测试板内和板外的阻抗,阻抗线长可以控制在40mm内,这样CAM制作时可以缩短阻抗测试条,提高板材利用率,特别是在昂贵的高频和高速板材的利用率上表现明显,可以为客户有效降低成本。

上一篇:PCB生产流程之湿区流程简介

下一篇:医疗设备HDI盲埋孔线路板

2025-03-12

2025-03-11

2025-03-11

2025-03-10

2025-03-10

2025-03-10

相关新闻