2025.06.20

2025.06.20PCB在5G通信中的核心作用

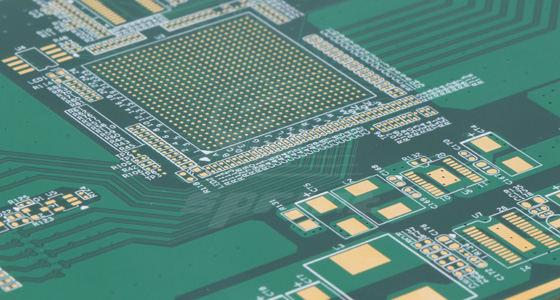

第五代移动通信技术(5G)以其高速率、低延迟和高连接密度的特点,正引领着通信技术的新一轮革命。在5G通信系统中,电路板也是不可或缺的存在,其性能直接影响到5G设备的整体表现。下面将探讨PCB在5G通信中的核心作用。

一、高频高速传输的基石

5G通信的高频段工作特性要求PCB材料具有优异的高频传输性能和低介电损耗。PCB作为信号传输的媒介,其材料和设计必须适应高达几十吉赫兹

当前位置:

当前位置: